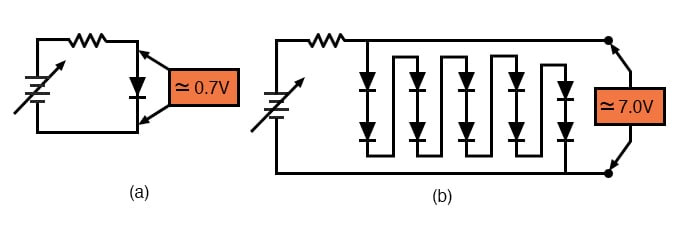

쇼트키 다이오드S 쇼트키 다이오드 는 PN 반도체 접합이 아닌 금속 -N 접합 으로 구성됩니다 . 핫 캐리어 다이오드라고도 하는 쇼트키 다이오드는 빠른 스위칭 시간(낮은 역회복 시간), 낮은 순방향 전압 강하(일반적으로 금속-실리콘 접합의 경우 0.25~0.4V), 그리고 낮은 접합 커패시턴스를 특징으로 합니다.쇼트키 다이오드의 회로도 기호는 아래 그림과 같습니다.쇼트키 다이오드 회로도 기호.쇼트키 다이오드의 장단점쇼트키 다이오드의 순방향 전압 강하(VF), 역방향 회복 시간(trr), 그리고 접합 커패시턴스(CJ)는 일반적인 "정류" 다이오드 보다 이상적인 값에 더 가깝습니다 . 따라서 고주파 애플리케이션에 적합합니다. 하지만 쇼트키 다이오드는 일반적으로 정류 다이오드보다 순방향 전류(IF)와 역방향 ..